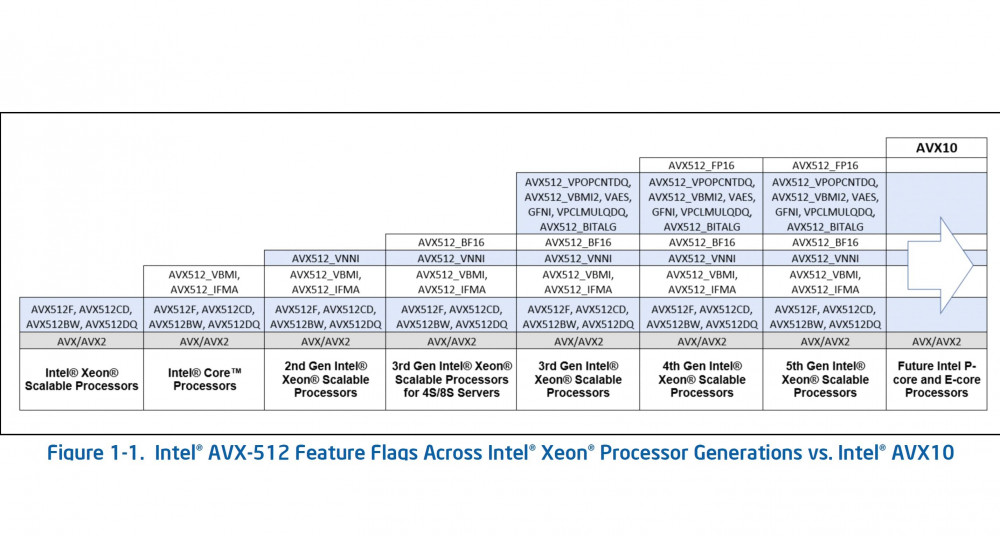

Intel Announces AVX10 ISA with AVX-512 Support for P-Cores and E-Cores

Intel is preparing to introduce its new Instruction Set Architecture - AVX10 ISA, which will feature AVX-512 support for both P-Cores and E-Cores.

According to the information posted by Twitter user, Longhorn, Intel's upcoming AVX10 ISA is likely to be launched in two versions: a pre-enablement (AVX10.1) and a post-enablement (AVX10.2). Both versions include support for optional 512-bit FP/int, which Intel decided to exclude from its latest client chips like Alder Lake and Raptor Lake.

However, Intel might reintroduce these instructions in processors that support the AVX 10 ISA. According to the pre and post-enablement details, the AVX10 ISA is part of the latest APX (Advanced Performance Extensions) and will offer:

- Optional 512-bit FP/int

- 128/256-bit FP/int

- 32 vector registers

- 8 mask registers

- 256/512-bit embedded rounding

- Embedded broadcast

- Scalar/SSE/AVX "promotions"

- Native media additions

- HPC additions

- Transcendental support

- Gather/Scatter

- Version-based enumeration

AVX-512 has not disappeared entirely, the support for these instructions still exists on the HPC side with the Xeon chips. However, on the client side, AVX-512 might make a comeback since AMD is already offering it on its Ryzen 7000 consumer processors, which have demonstrated impressive performance capabilities in specific workloads without a significant increase in power consumption.

In addition, the pre-enablement AVX10.1 version only offers AVX-512 support for the P-Cores, while the AVX10.2 version adds it for E-Cores as well.

Intel has stated that future Xeon processors, codenamed Granite Rapids, will be the first to be compatible with AVX10 and will mark the transition from AVX-512 to Intel AVX10 (excluding 256-bit vector extensions).